免责声明:文章转载自《【转】Xilinx FPGA ChipScope的ICON/ILA/VIO核使用》仅用于学习参考。如对内容有疑问,请及时联系本站处理。

上篇分布式环境下限流方案的实现redis RateLimiter Guava,Token Bucket, Leaky BucketPhpStorm快捷键设置/个性化设置,下篇

宿迁高防,2C2G15M,22元/月;香港BGP,2C5G5M,25元/月 雨云优惠码:MjYwNzM=

创建对话框主要分两大步,第一,创建对话框资源,主要包括创建新的对话框模板、设置对话框属性和为对话框添加各种控件;第二,生成对话框类,主要包括新建对话框类、添加控件变量和控件的消息处理函数等。鸡啄米在本节中先讲讲怎样创建对话框模板和设置对话框属性。 创建基于对话框的应用程序框架 之前鸡啄米创建的HelloWorld程序是单文...

一时冲动,跑步进入了FPGA的大门,尤老师是教练,我之前一直做嵌入式软件,数字电路也是十年前大学课堂学过,早已经还给老师了。FPGA对于我来说完全是小白,所以。老师的课程,对于我来说至关重要!因为见过太多从入门到放弃的案例了! 什么样的教程和视频,可以不至于让小白从入门到放弃呢?我总结了几点:1.由浅入深,循序渐进,不急躁,不跃进,符合人的认知规律...

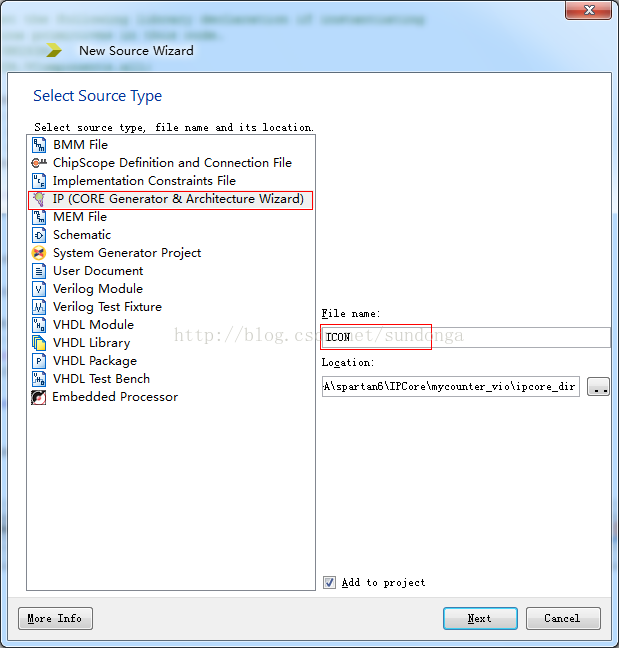

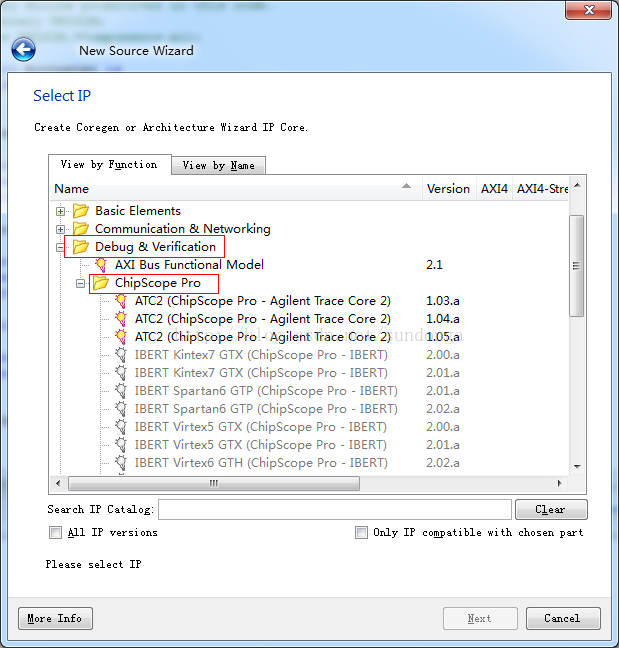

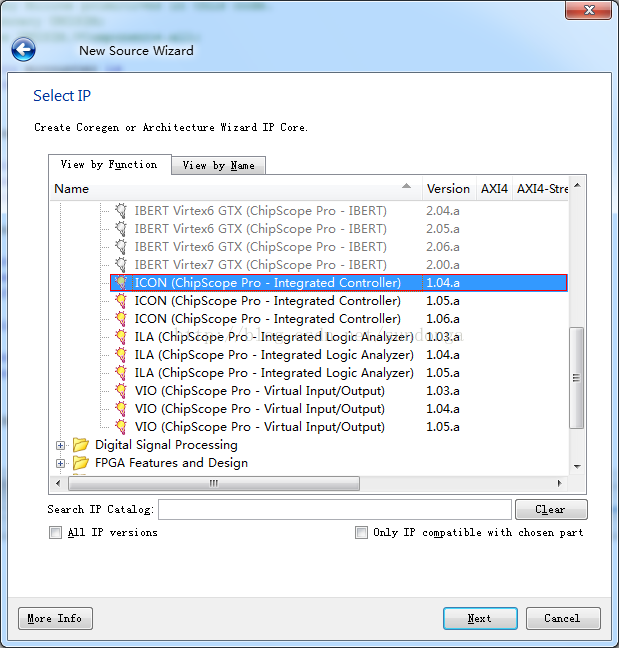

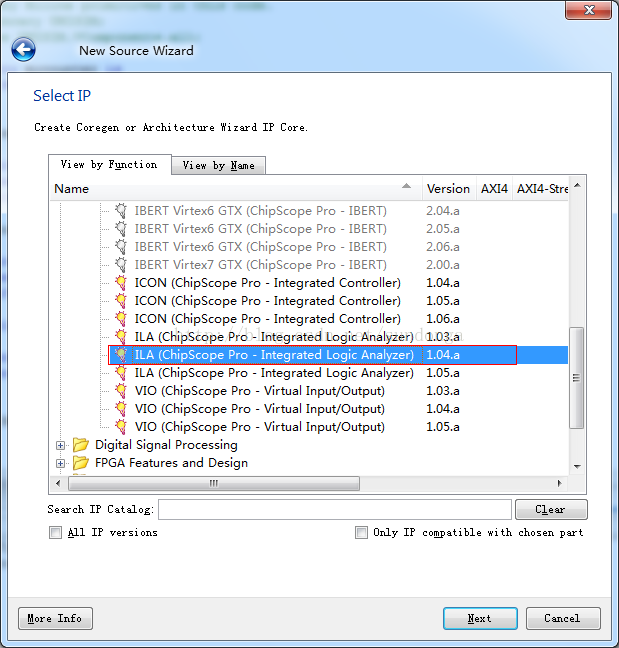

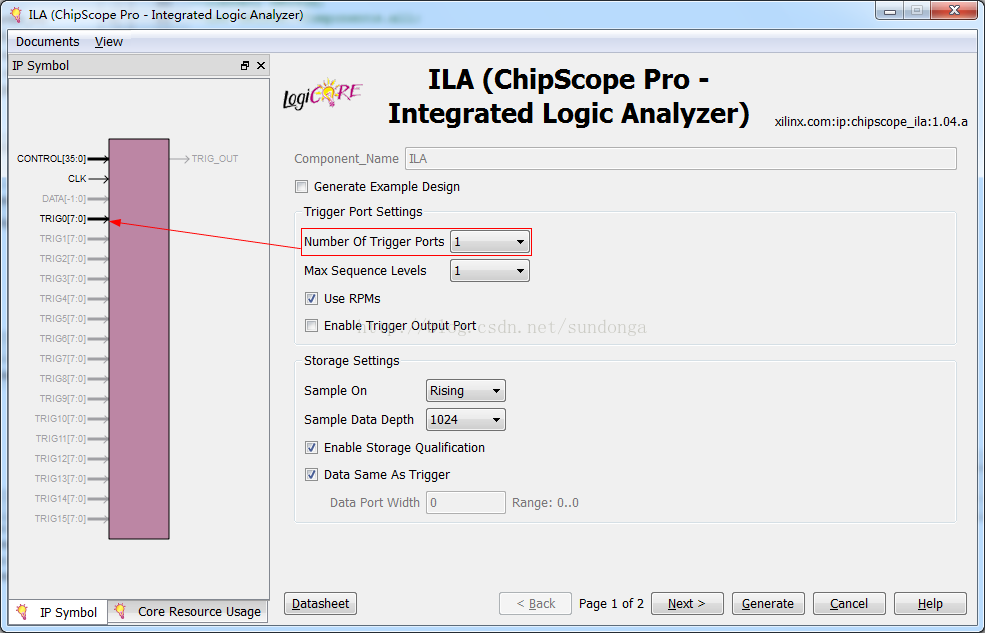

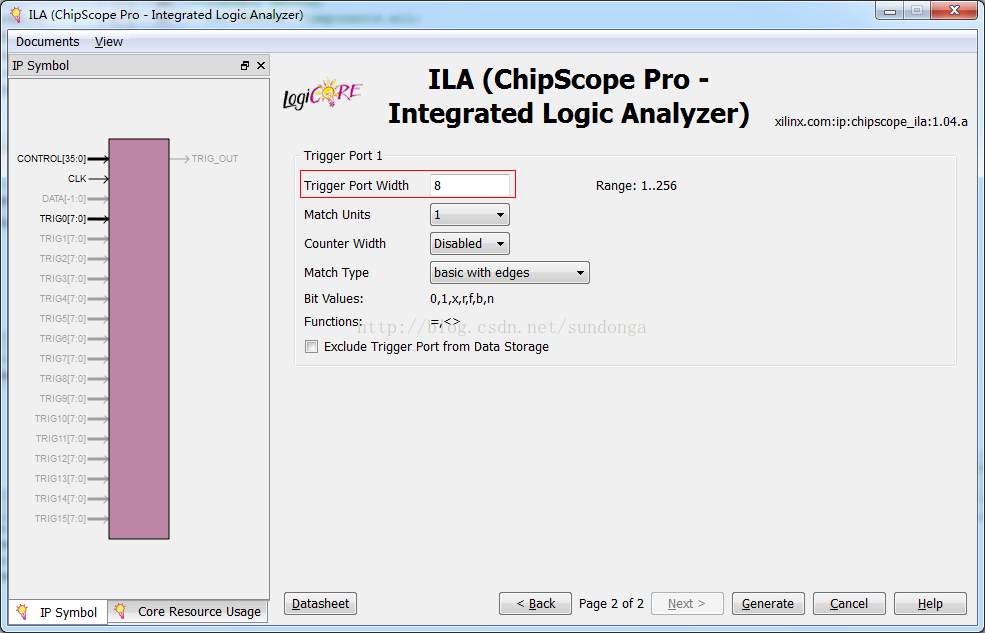

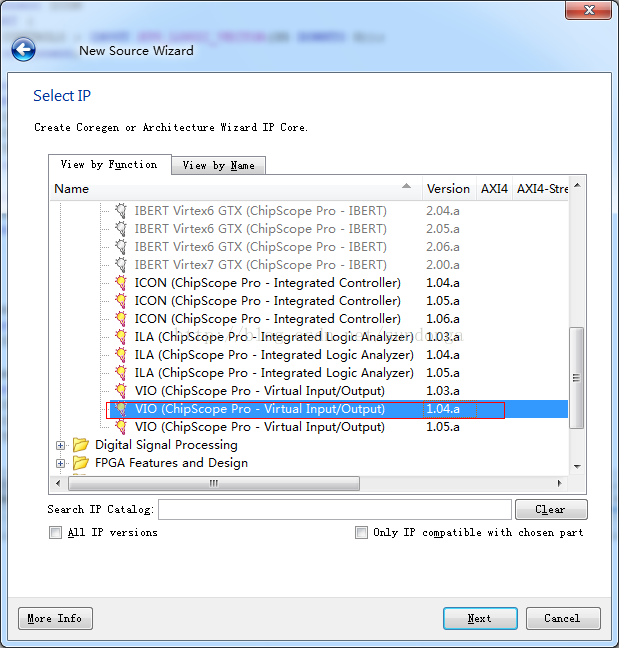

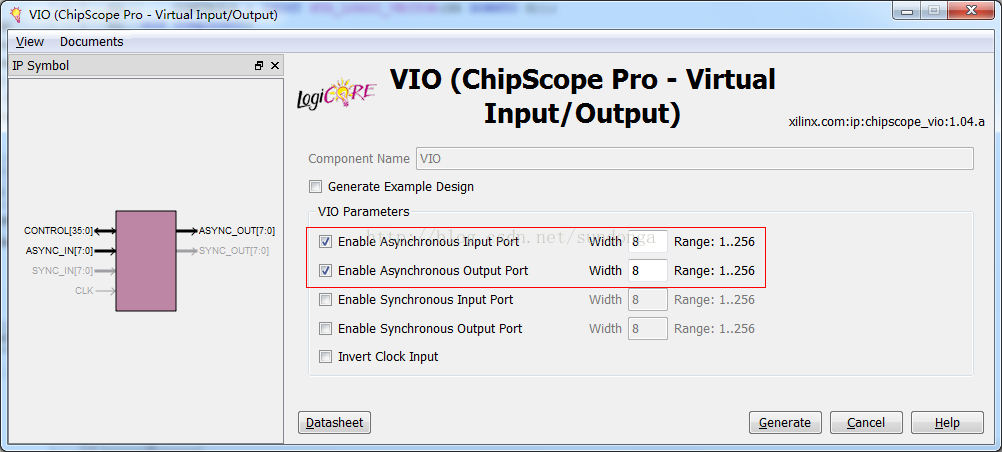

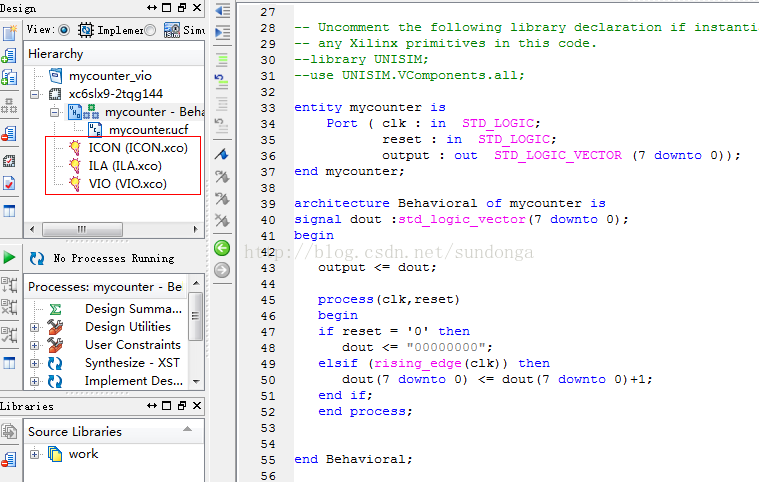

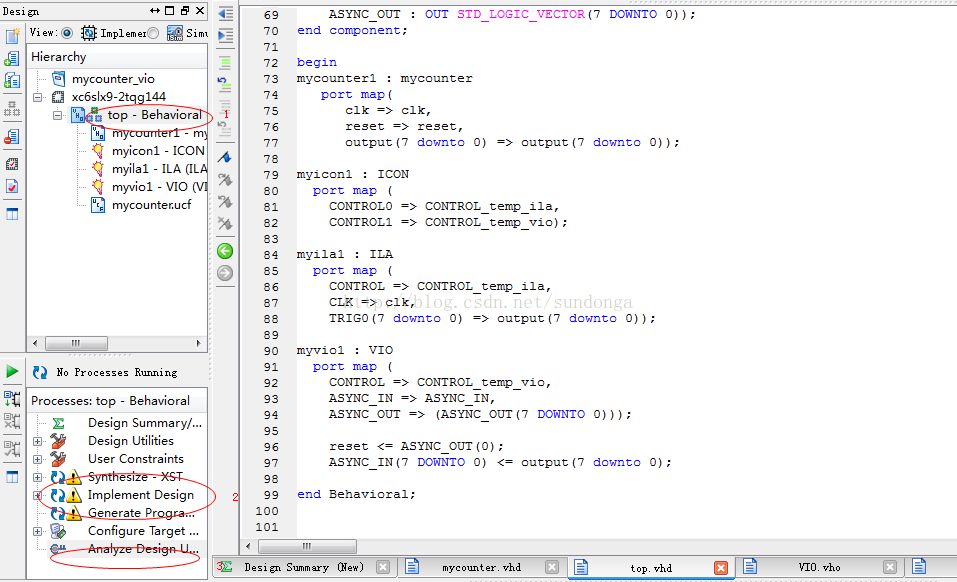

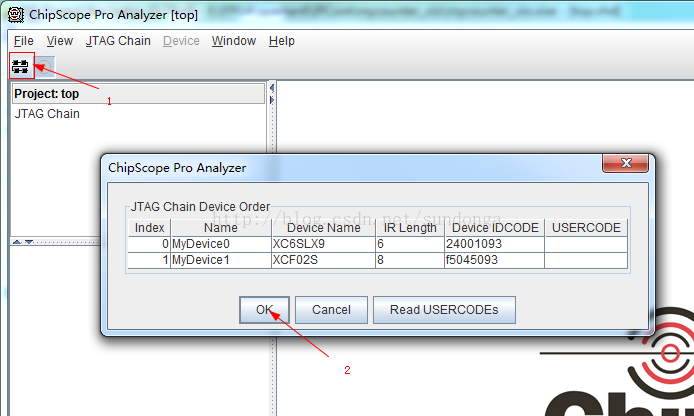

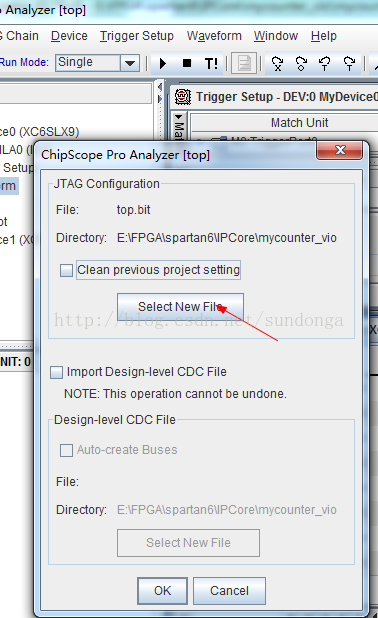

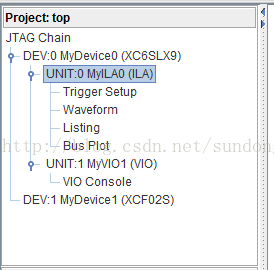

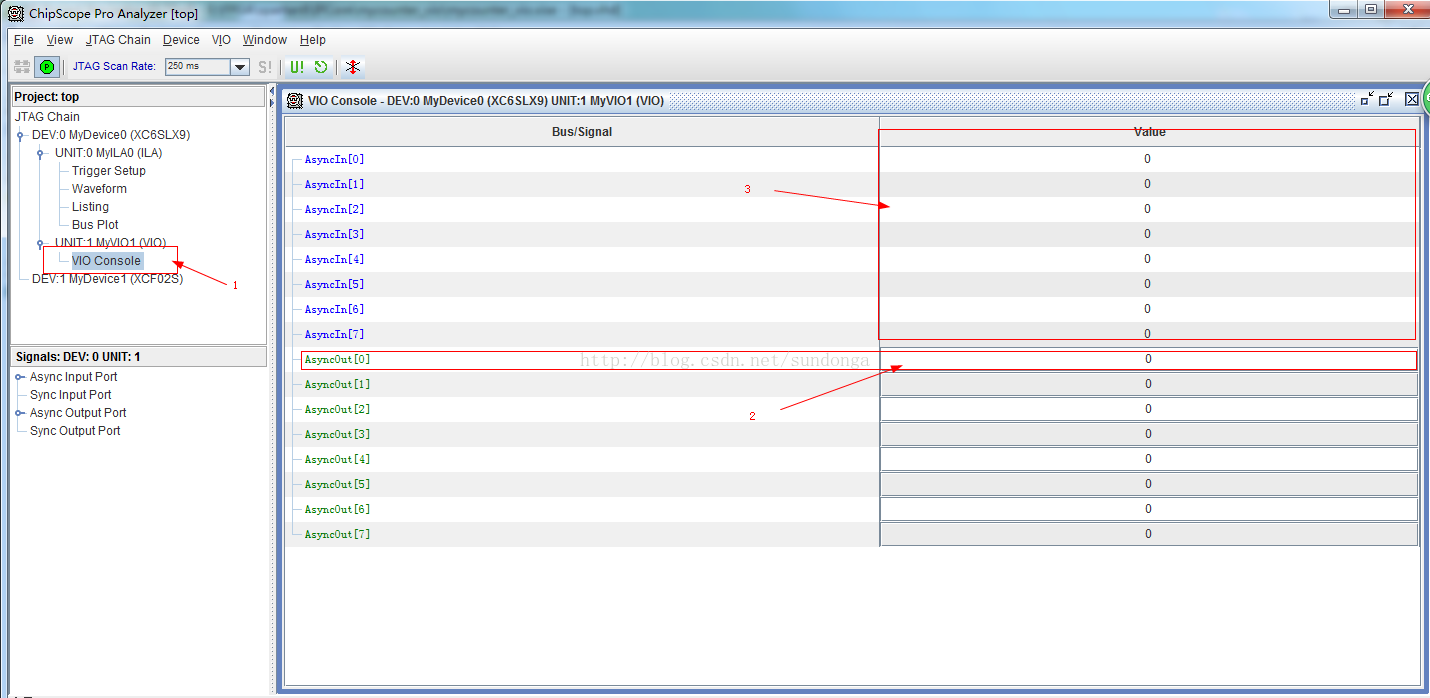

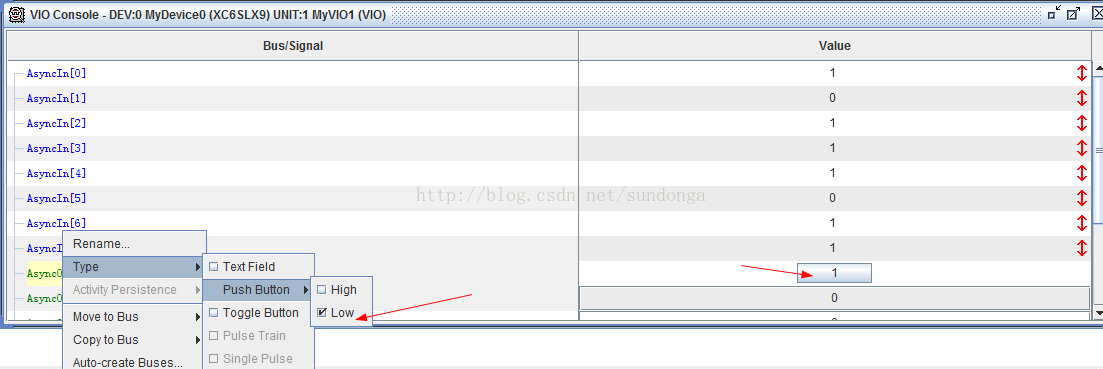

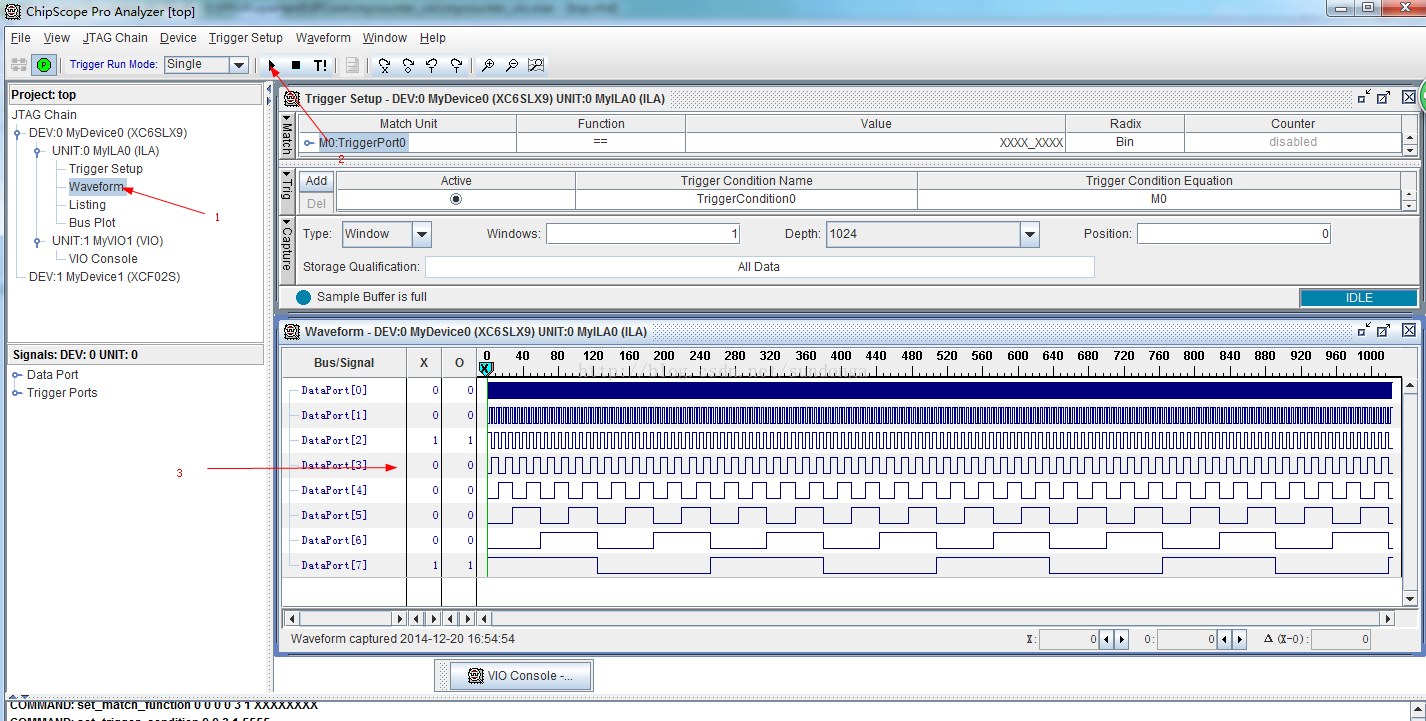

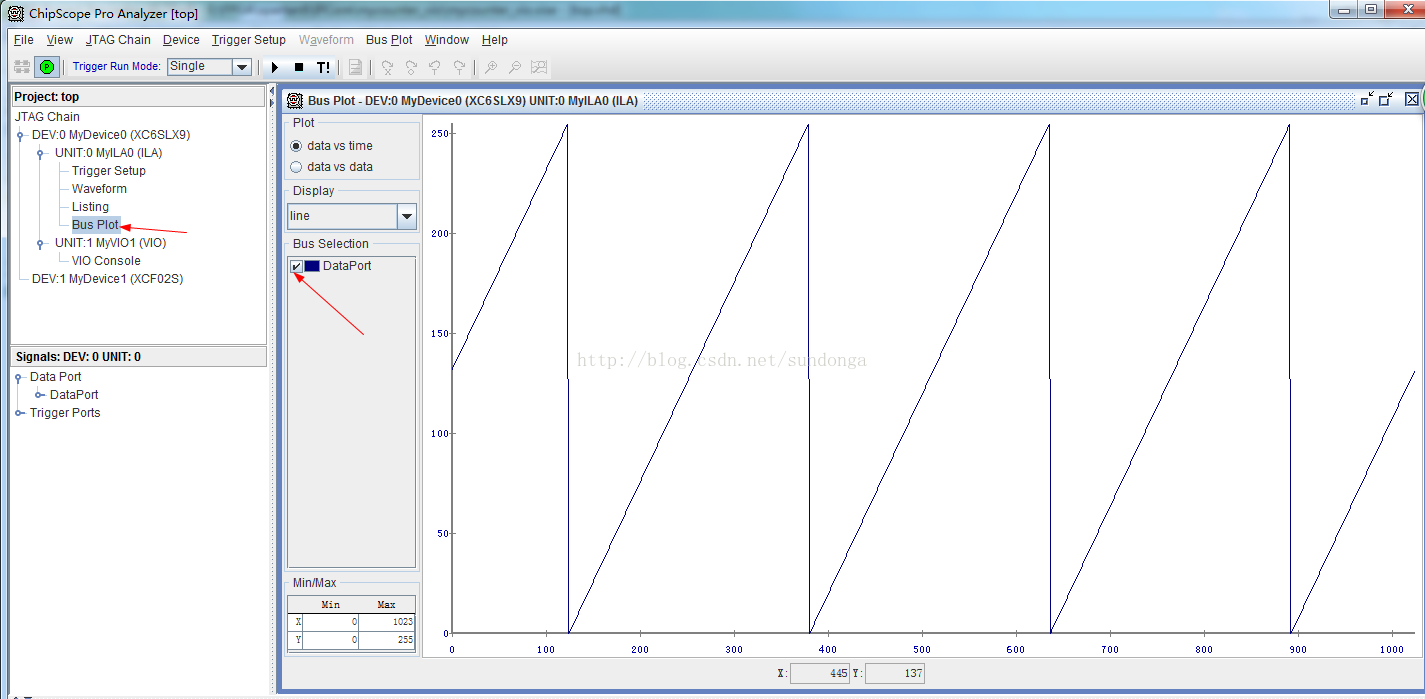

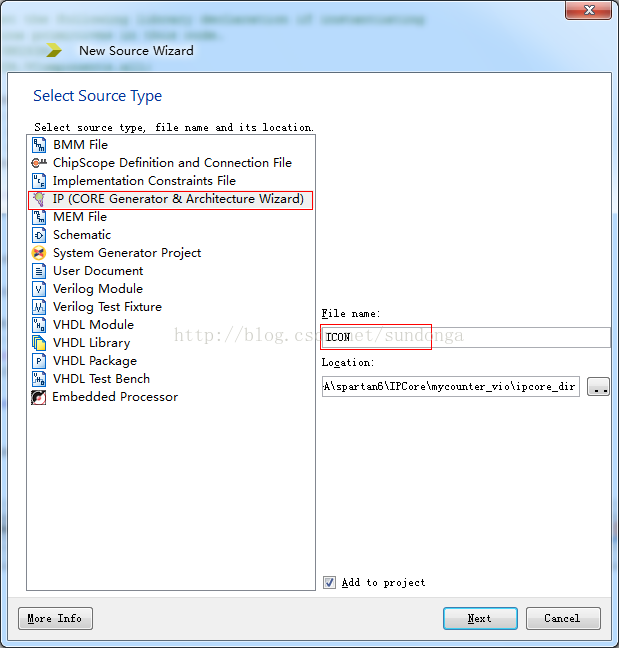

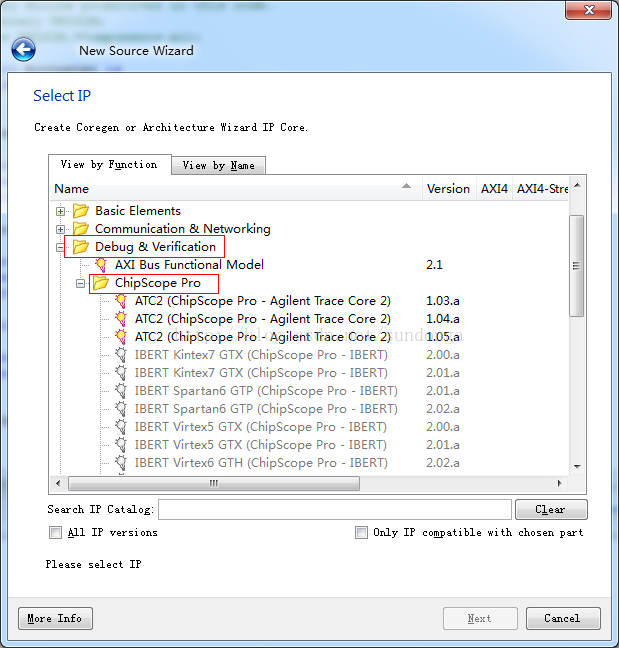

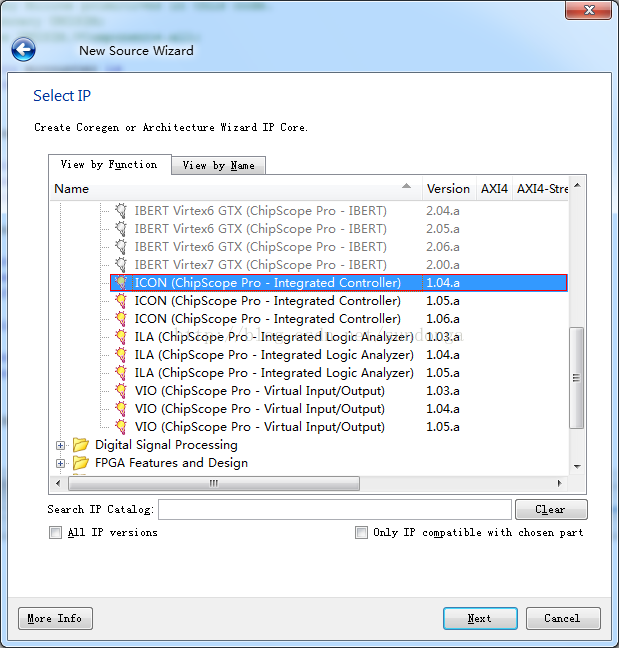

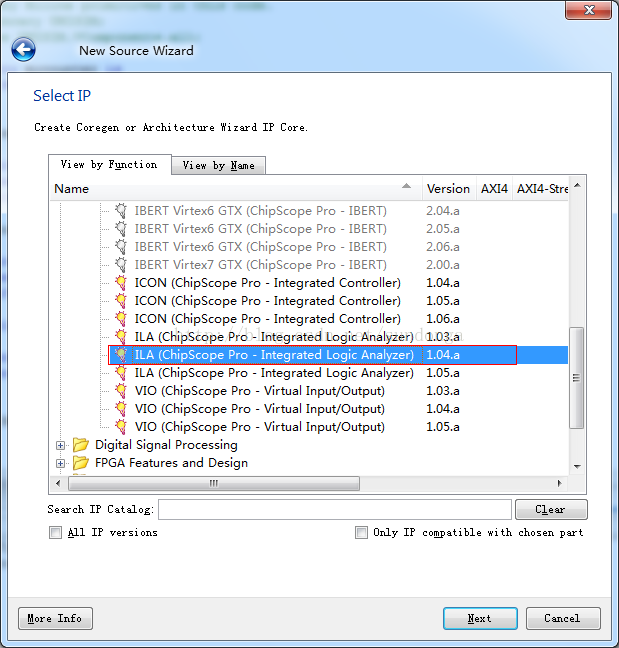

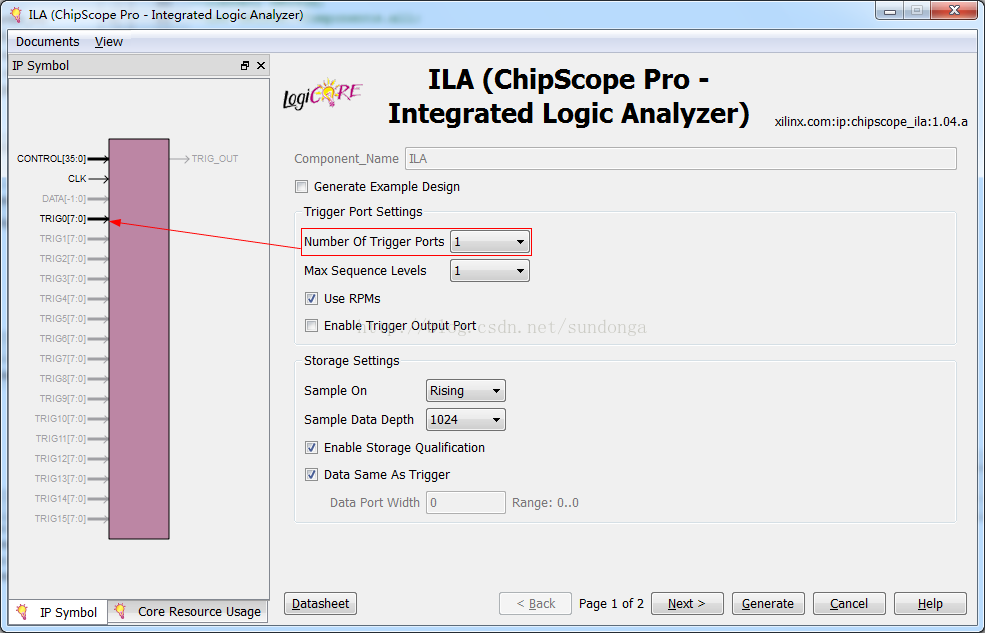

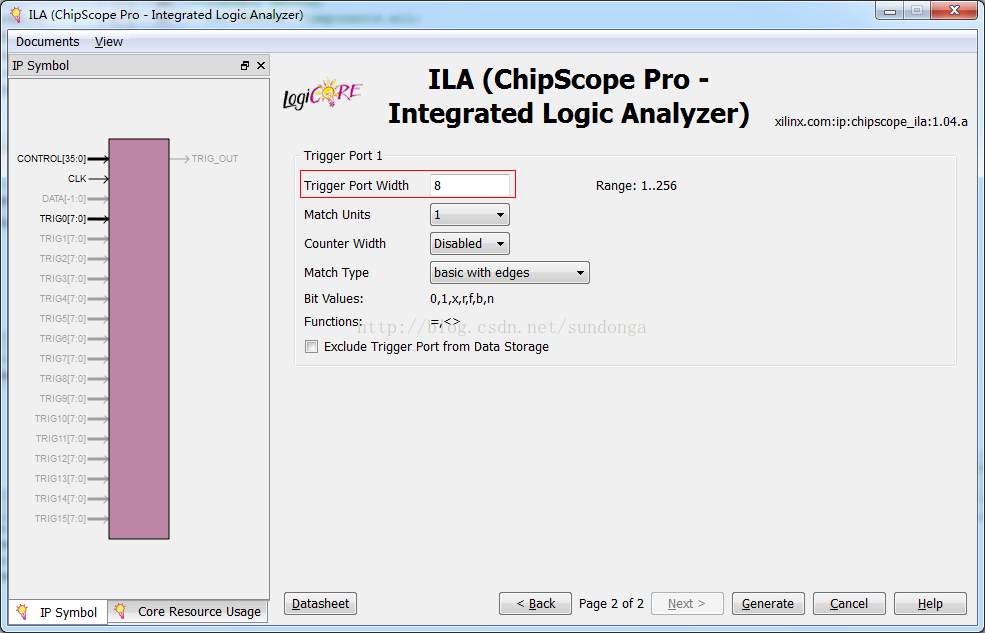

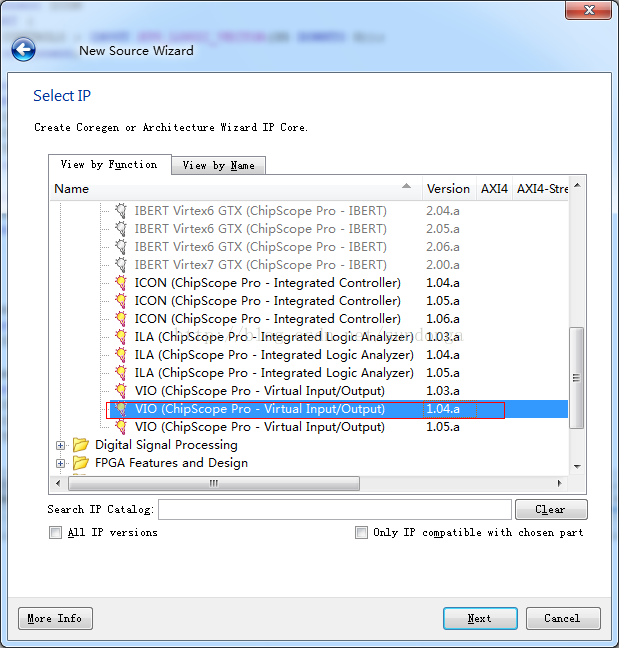

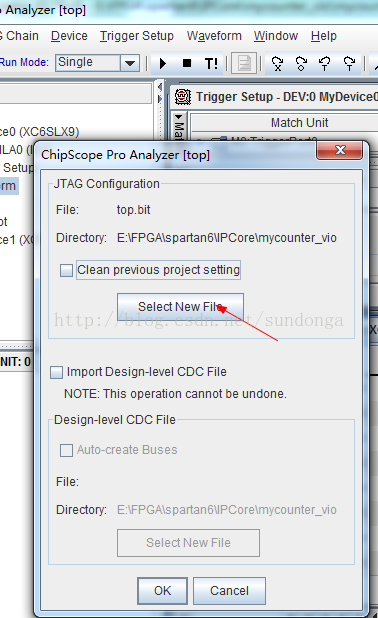

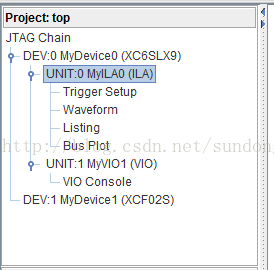

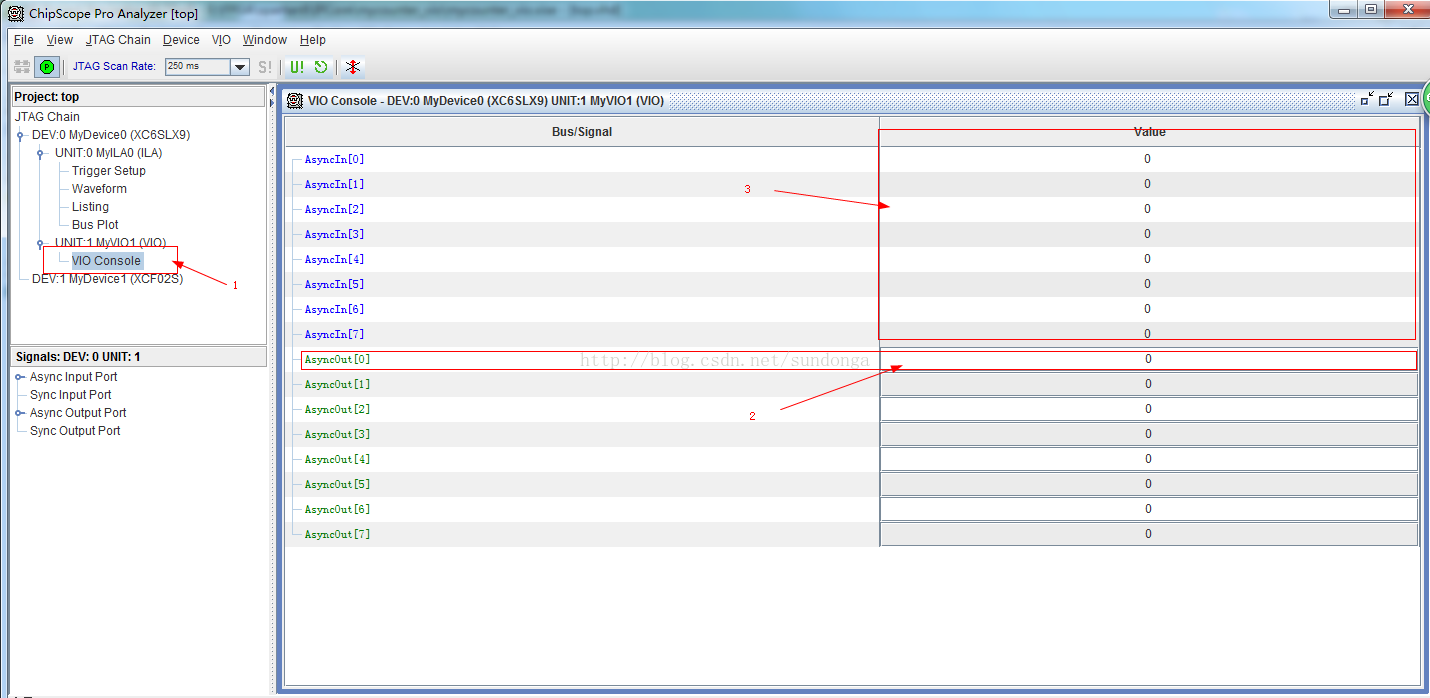

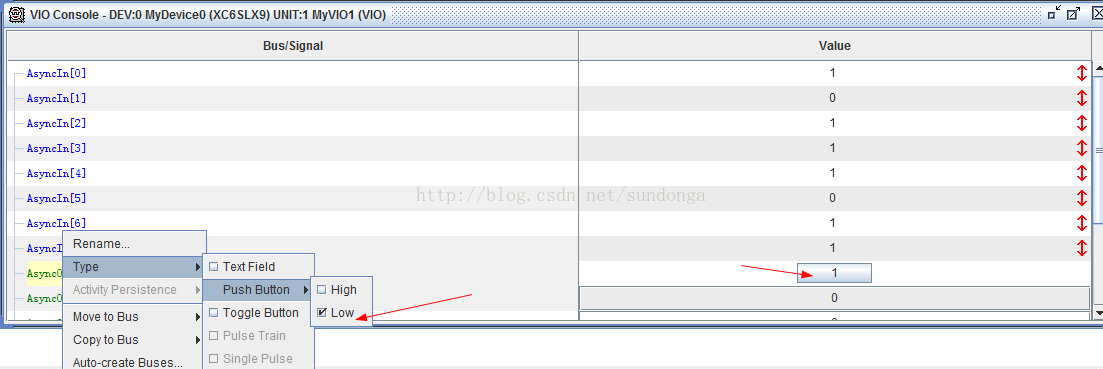

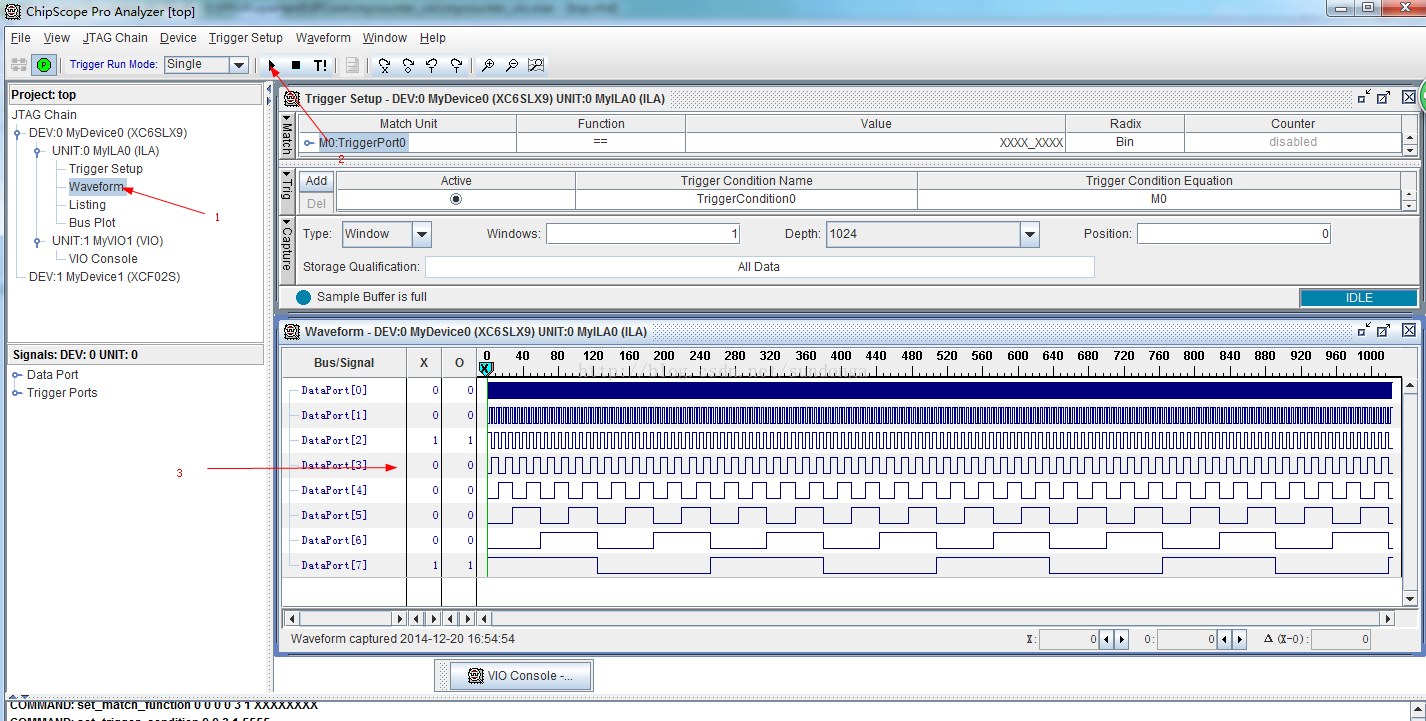

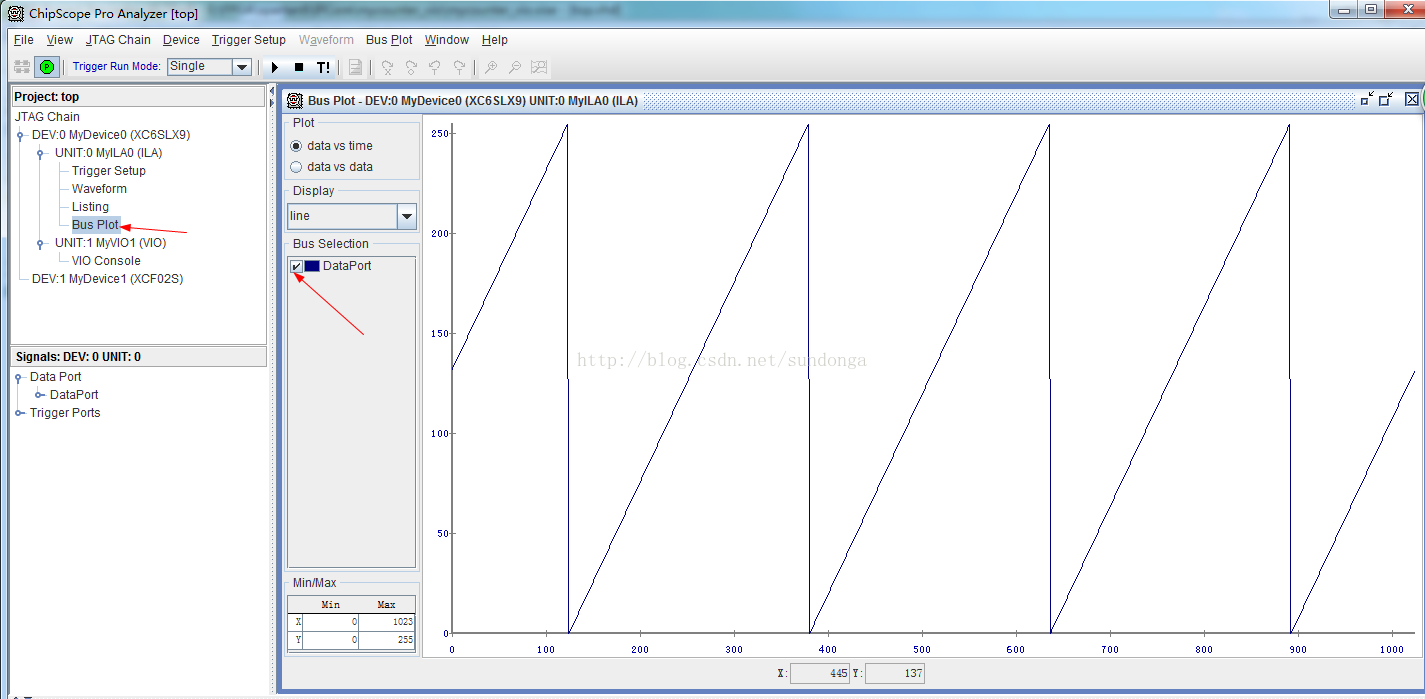

基本步骤是:写完.v文件后开始综合Synthesize;然后打开PlanAhead-Post Synthesis分配引脚(会自动添加.ucf文件);若要使用ChipScope,则New一个.cdc文件(ChipScope Definition and Connection File),Trigger Width用于设置共有几个被观察信号,Data Dept...

https://zhuanlan.zhihu.com/p/154156003 1. 介绍 由于在自动驾驶领域需要对传感器的数据作大量的基于深度内神经网络的复杂运算,GPU和FPGA被不约而同地用来作为对CPU的一种加速器被使用。这样做不仅可以提高计算性能,并且可以大幅度地降低能耗。FPGA+CPU架构的自动驾驶平台凭借其灵活性,高效率,低能耗等特点,正越...

在ModelSim中添加Xilinx仿真库 说明: l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下。如作者是安装在D:softwaresModelsim目录下。 l ISE软件也最好安装在不带空格的目录下。 1、找到开始菜单->程序->Xilinx ISE Design Suite 11 -&...

在软件安装之前,得准备好软件安装包,可从Xilinx官网上下载: http://china.xilinx.com/support/download/index.html/content/xilinx/zh/downloadNav/design-tools.html。 下载好的软件如下所示: 接下来开始安装ISE14.7软件: (1)在安装包目录下双...