写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文!

本博客全网唯一合法URL:http://www.cnblogs.com/acm-icpcer/p/9291767.html

1.指令集设计:

CPU的指令类型根据其操作的不同,可以分为下面七类。

(1)计算类指令(Computational)

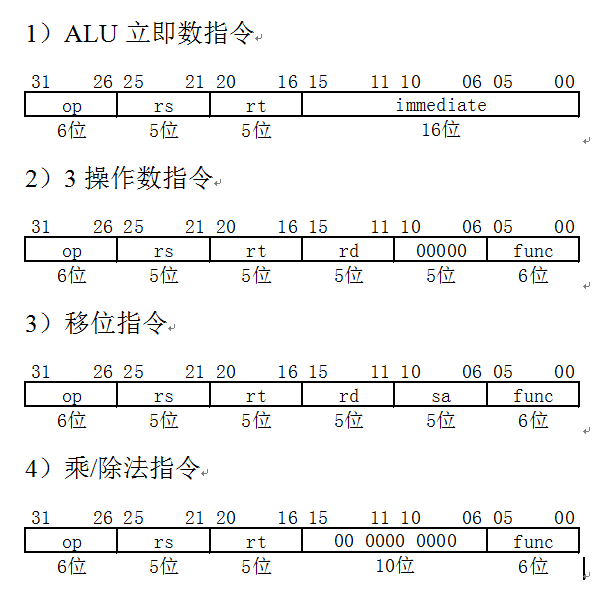

计算类指令用于执行算术操作,乘/除,逻辑操作和对寄存器进行移位操作。这些指令有两种类型:寄存器类型和立即数类型。寄存器类型的指令使用两个源寄存器的值作为源操作数,立即数类型使用一个寄存器和立即数作为源操作数。根据操作的不同,这些指令分为下面4种:

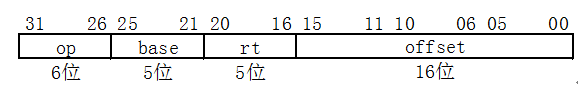

(2)Load/Store指令

Load和Store指令都为立即数(I-type)类型,用来在存储器和通用寄存器之间的储存和装载数据。值得一提的是MIPS指令集只有该类指令访问内存,而其他指令都在寄存器之间进行,所以指令的执行速度较高。该类指令只有基址寄存器的值加上扩展的16位有符号立即数一种寻址模式,数据的存取方式可以是字节(byte)、字(word)和双字(Double word)。

指令格式:

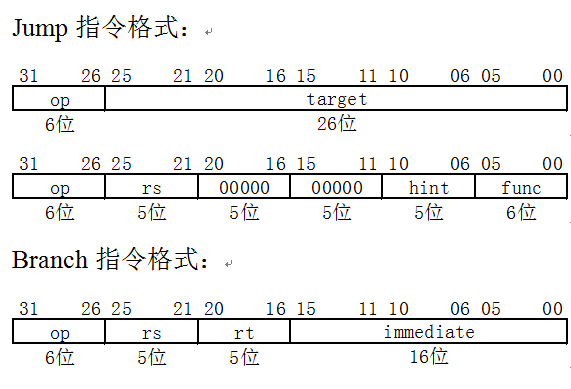

(3)跳转/分支指令(jump & branch)

跳转和分支指令改变程序流。所有的跳转和分支指令都会产生的一个延迟槽(delay slot)。紧跟着跳转/分支指令后的指令(delay slot中的指令)也被执行,然后在跳转目的的第一条指令从存储器中取出并执行,这是在指令的流水线执行时获得更高效率。

(4)寄存器传送指令

寄存器传送指令用来在系统的通用寄存器(GPR)、乘除法专用寄存器(HI、LO)之间传送数据,这些指令分为有条件传送和无条件传送2种类型。

(5)专用指令

专用指令用来产生软件中断,当执行这类指令的时候,CPU产生异常并转入中断处理程序。这些指令有系统调用(Syscall),暂停(Break)和Trap指令等,主要用于软件的异常处理。

(6)协处理器指令

协处理器指令对协处理器进行操作。协处理器的Load和Store指令是立即数类型,每个协处理器指令的格式依协处理器不同而不同。

(7)系统控制协处理器(CP0)指令

系统控制协处理器(CP0)指令执行对CP0寄存器的操作来控制处理器的存储器并执行异常处理。

本实验设计只选取了20条典型的MIPS指令来描述CPU逻辑电路的设计方法。下表列出了本实验的所涉及到的20条MIPS指令。

20条MIPS指令

R型指令 | |||||||

指令 | [31:26] | [25:21] | [20:16] | [15:11] | [10: 6] | [5:0] | 功能 |

Add | 000000 | rs | rt | rd | 000000 | 100000 | 寄存器加 |

Sub | 000000 | rs | rt | rd | 000000 | 100010 | 寄存器减 |

And | 000000 | rs | rt | rd | 000000 | 100100 | 寄存器与 |

Or | 000000 | rs | rt | rd | 000000 | 100101 | 寄存器或 |

Xor | 000000 | rs | rt | rd | 000000 | 100110 | 寄存器异或 |

Sll | 000000 | 00000 | rt | rd | sa | 000000 | 左移 |

Srl | 000000 | 00000 | rt | rd | sa | 000010 | 逻辑右移 |

Sra | 000000 | 00000 | rt | rd | sa | 000011 | 算术右移 |

Jr | 000000 | rs | rt | rd | 000000 | 001000 | 寄存器跳 |

I型指令 | |||||||

Addi | 001000 | rs | rt | immediate | 立即数加 | ||

Andi | 001100 | rs | rt | immediate | 立即数与 | ||

Ori | 001101 | rs | rt | immediate | 立即数或 | ||

Xori | 001110 | rs | rt | immediate | 立即数异或 | ||

Lw | 100011 | rs | rt | offset | 取数据 | ||

Sw | 101011 | rs | rt | offset | 存数据 | ||

Beq | 000100 | rs | rt | offset | 相等转移 | ||

Bne | 000101 | rs | rt | offset | 不等转移 | ||

Lui | 001111 | 00000 | rt | immediate | 设置高位 | ||

J型指令 | |||||||

J | 000010 | address | 跳转 | ||||

Jal | 000011 | address | 调用 | ||||

R型指令的op均为0,具体操作由func指定。rs和rt是源寄存器号,rd是目的寄存器号。移位指令中使用sa指定移位位数。

I型指令的低16位是立即数,计算时需扩展到32位,依指令的不同需进行零扩展和符号扩展。

J型指令的低26位是地址,是用于产生跳转的目标地址。

2.总体电路设计:

本实验所设计的单周期CPU的总体电路结构如图所示。

本实验所设计的CPU主要组成部分有:运算器(ALU)、控制器(Control Unit)、寄存器堆(Register Files)、取指电路及相关基础部件(如选择器)等构成。

具体的代码实现请看:

Verilog HDL语言实现的单周期CPU设计(全部代码及其注释)

tz@COI HZAU

2018/7/10