欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章

硬件加速是指利用硬件模块来替代软件算法以充分利用硬件所固有的快速特性。

硬件加速实质上是通过增加运算并行性达到加速的目的的。

常常采用流水线和硬件复制的方法。

1 流水线1.1 适合流水线的场景

如果某个设计的处理流程分为若干步骤,而且整个数据处理是“单向流”的,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计的方法来提高系统的工作频率。

流水线的各个步骤处理由功能单一的各个单元完成,当数据沿着流水线方向依次通过所有功能单元时,即完成了所有的数据处理并输出。

由于流水线上各个功能单元能够并行工作,故只要保证下一功能单元的输入是上一功能单元的输出,则所有功能单元并行工作可以保证整个流水线的正常工作,而无需等到整个流水线吹了结束后才开始下一份数据的处理,进而保证数据充满了所有功能单元,提高了处理速率。

1.2 使用流水线的原因

所谓流水线(pipeline)设计,以汽车工业中的 流水生产线 举例说明。

在汽车生产的时候,假设分为 5 个阶段,每个阶段都需要 1 个工人花费 1 小时完成,因为后续的阶段必须等前面阶段完成后才能进行,所以如果一个人来工作时,总共需要 5 个小时才能完成一辆汽车。采用流水线方式,即在生产线上安排5个人每人负责一个阶段的任务,在进行后续阶段时,前面的阶段可以进行新的工作,那么每个小时都可以生产出一辆汽车了,生产效率提高了 5 倍。

可以看到,流水线之所以可以大大提高效率的原因在于:传统的方式,某个阶段进行时,其他阶段是空闲等待的,浪费时间;而流水方式中,在处理后续阶段时,前面的阶段可以进行新的加工,每时每刻,每个工人都是在工作的,这就是流水线能提高生产效率的原因。

在电路上第一种方法就是总共有一个寄存器(reg1),单第二种方法会使用五个寄存器(reg1、reg2、reg3、reg4、reg5)

流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法。

目的是将一个大操作分解成若干的小操作,每一步小操作的时间较小,所以能提高频率,各小操作能并行执行,所以能提高数据吞吐率(提高处理速度)。

1.3 简单的流水线例子

采用流水设计的方法就是:在较长的组合逻辑路径中插入 DFF(D触发器),将其分割为几个小的组合逻辑,新的 Tlogic 显然小于原来的 Tlogic,所以系统的时钟频率就可以提高了。

举例来说明:设计一个电路完成 i = (a + b + c + d) + (e + f + g + h) 运算。

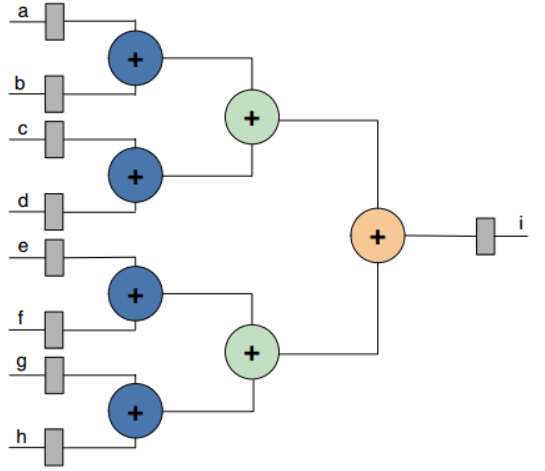

下面是没有流水的设计:

第一级 DFF 到第二级 DFF 之间数据路径的时延为:

Tff

= Tco + Tlogic

= Tco + 3*Tadder

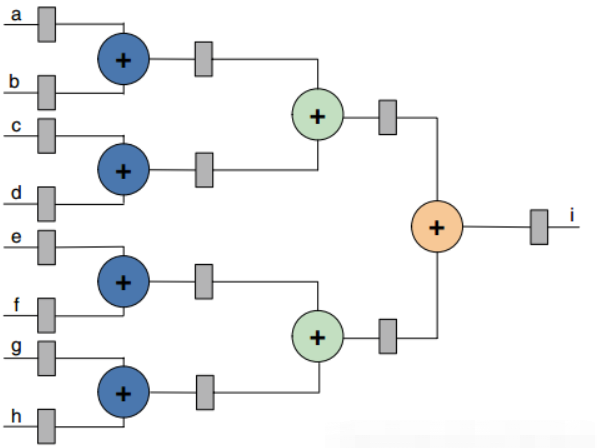

下面是插入两级流水的设计:

现在相邻的两级 DFF 之间的组合逻辑只有 1 级加法器,而不是原来的 3 级,这时数据路径的时延为:

Tff = Tco + Tlogic

= Tco + Tadder

显然,采用流水后 Tff 更小,系统能够达到的工作时钟频率也就更高。数据传输时除了第一个数据的所耗时间为3*Tff ,其它数据所用时间均为Tff。

2 硬件复制在某些FPGA设计中,需要很多重复设计的时候,这时候逻辑复制也就有用了。逻辑复制也可以说是并行计算,简单的说就是把相同的计算进行堆积,提高单位周期内的计算吞吐能力。

针对现在的神经网络计算展开说明硬件复制的高效之处。

比如说一个 3*3*ic*oc 的卷积核(kernel)对特征图(input feature map)进行卷积操作,即对应位置的点进行相乘相加计算,得出一个通道所有的点的计算过程,需要拿 同一个特征图 和 oc个不同的3*3*ic卷积核 进行相同,因为计算模式相同,所以可以采取硬件复制的方式。

这样,就是等于复制了 oc 个计算模块,同时进行 oc 个并行计算,一次计算得到 oc 个输出。

3 总结利用流水线的设计方法,可大大提高系统的工作速度。

这种方法可广泛运用于各种设计,特别是大型的、对速度要求较高的系统设计。

虽然采用流水线会增大资源的使用,但是它可以降低寄存器间的传播延时,保证系统维持高的系统时钟速度。

在实际应用中,考虑到资源的使用和速度的要求,可以根据实际情况来选择流水线的级数以满足设计需要。

这是一种典型的以面积换速度的设计方法。这里的“面积”主要是指设计所占用的FPGA逻辑资源数目,即利用所消耗的触发器(FF)和查找表(LUT)来衡量。“速度”是指在芯片上稳定运行时所能达到的最高频率。面积和速度这两个指标始终贯穿着FPGA的设计,是设计质量评价的最终标准。