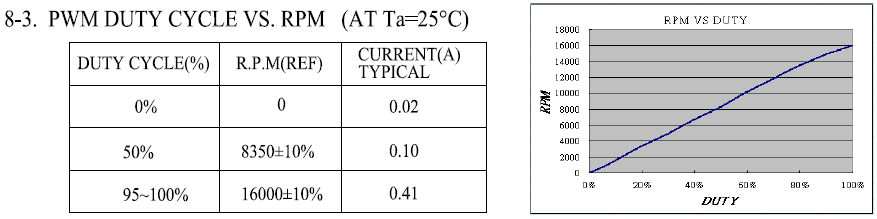

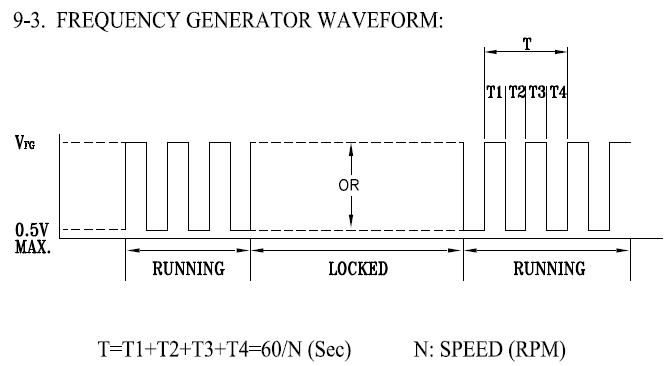

1、风扇最大转速16000RPM,那么每一转需要时间60S/16000=0.00375S=375*10^4ns=T=T1+T2+T3+T4;

2、采样0.6S内的风扇detect信号的上升沿个数:0.6s/(375*10^4ns)=0.6*10^9ns/(375*10^4ns)=160

由于转数取最大值,所以T是最小的,那么160是最大计数个数,实际风扇规格书中的一转有两个周期,所以最大计数达到320(不考虑最大值16000RPM的±10%波动),那么需要位宽为9的二进制计数器。

在实际换算中,获得的计数temp0需要除以2,然后乘以100,得到采样到的RPM。

公式:采样RPM=temp0/2*100

x14_out是8位位宽的寄存器,那么可以定义temp0为[8:0],然后取值[8:1],这样可以相当于除以2,并且保证了temp0计数不会溢出。那么实际中得到的x14_out值需要转换成十进制后乘以100就ok。

实际公式:采样RPM=temp0*100

注:clk为25MHz的时钟。

注:AVC(型号:DBTA0420B2UP011)

VHDL程序:

1 libraryIEEE; 2 use IEEE.STD_LOGIC_1164.ALL; 3 use IEEE.STD_LOGIC_ARITH.ALL; 4 use IEEE.STD_LOGIC_UNSIGNED.ALL; 5 6 entity x14_fan_speed_det0 is 7 port( 8 x14_out : out std_logic_vector(7 downto 0); 9 reset : in std_logic; 10 clk : in std_logic; 11 fan_det_0 : in std_logic 12 ); 13 endx14_fan_speed_det0; 14 15 architecture rtl of x14_fan_speed_det0 is 16 17 signal temp0 : std_logic_vector(8 downto 0); 18 signal count0 : std_logic_vector(23 downto 0); 19 20 begin 21 22 process(count0,fan_det_0) 23 begin 24 if (count0= "000000000000000000000000") then 25 temp0 <= "000000000"; 26 elsif( fan_det_0'event and fan_det_0 = '1')then 27 temp0 <= temp0 + '1'; 28 end if; 29 end process; 30 31 32 process(reset,clk) 33 begin 34 if (reset = '0') then 35 count0 <= "000000000000000000000000"; 36 x14_out <= x"00"; 37 elsif (clk'event and clk= '1') then 38 if (count0= "111001001110000111000000") then ---计数15000000 0.6S 39 count0 <= "000000000000000000000000"; 40 x14_out <= temp0(8 downto 1); 41 else 42 count0 <= count0 + '1'; 43 --x14_out <=x14_out; 44 end if; 45 end if; 46 end process; 47 48 end rtl;