软件版本:VIVADO2017.4

操作系统:WIN7/WIN10 64bit

硬件平台:XILINXFPGA MK7160FA

米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!!

1.1 课程介绍

这一章开始主要介绍XILINX FPGA PICE IP XDMAIP的使用。XDMA IP使用部分教程分LINUX 篇和WINDOWS篇两个部分。通过实战,面向应用,提供给大家 XILINX FPGA PCIE 应用解决方案。

本教程以MK7160FA作为样机测试。在正式开始教程内容前,有必要把MK7160FA开发板的特点说明下。这是一款高性价比的FPGA开发板。带PCIE接口,四路SFP光通信接口,双路千兆以太网口,1路HDMI输入,1路HDMI输出,1路串口,1路USB3.0接口。支持MSXBO(米联客)FEP标准扩展接口。采用的CPU型号为XC7K160t-FGG676。PL端搭载64bit 2GB DDR3内存,FPGA读写PL端DDR支持的最大数据时钟为1600M,可以进行更多复杂的开发任务。

教程的内容完全适合其他开发板。如果读者使用过程中遇到问题,可以在我们讨论课程网页留言(米联客(MSXBO)论坛www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问)。我们会在论坛上公布相关课程内容和源码。

1.2 XDMA 概述

Xilinx 提供的DMASubsystem for PCIExpressIP是一个高性能,可配置的适用于PCIE2.0,PCIE3.0 的SG 模式DMA,提供用户可选择的AXI4 接口或者AXI4-Stream接口。一般情况下配置成AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,通常情况都会使用到DDR,AXI4-Stream 接口适用于低延迟数据流传输。

XDMA 是SGDMA,并非Block DMA,SG 模式下,主机会把要传输的数据组成链表的形式,然后将链表首地址通过BAR 传送给XDMA,XDMA 会根据链表结构首地址依次完成链表所指定的传输任务。

1.3 XDMA 提供如下接口:

- AXI4、AXI4-Stream,必须选择其中一个,用来数据传输

- AXI4-Lite Master,可选,用来实现PCIE BAR 地址到AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄

存器

- AXI4-Lite Slave,可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问XDMA

内部寄存器,不会映射到BAR

- AXI4 Bypass 接口,可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

1.4 XDMA IP 配置

Mode:配置模式,选择Advanced 高级配置

Lane Width:MK7160FA 支持X4

Max Link Speed:选择5.0GT/s 即PCIE2.0

Reference Clock :100MHZ,参考时钟100M

DMA Interface Option:接口选择AXI4 接口

AXI Data Width:128bit,即AXI4 数据总线宽度为128bit

AXI Clock :125M,即AXI4 接口时钟为125MHZ

PCIE ID 配置

PCIE BAR 配置,这里面的配置比较重要

首先使能PCIE to AXI Lite Master Interface ,这样可以在主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他AXI4-Lite 总线设备

映射空间选择1M,当然用户也可以根据实际需要来自定义大小。

PCIE to AXI Translation:这个设置比较重要,通常情况下,主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的,这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧BAR 地址为0,IP 里面转换设置为0x80000000,则主机访问BAR 地址0 转换到AXI LIte 总线地址就是0x80000000

DMA Bypass 暂时不用

PCIE 中断设置

User Interrupts:用户中断,XDMA 提供16 条中断线给用户逻辑,这里面可以配置使用几条中断线。

Legacy Interrupt:XDMA 支持Legacy 中断

选择MSI 中断

注意:MSI 中断和MSI-X 中断只能选择一个,否则会报错,如果选择了MSI 中断,则可以选择Legacy 中断,如果选择了MSI-X 中断,那么MSI 必须取消选择,同时Legacy 也必须选择None。此IP 对于7 系列设置有这么个问题,如果使用Ultrascale 系列,则可以全部选择

配置DMA 相关内容

Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道数,对于PCIE2.0 来说最大只能选择2,也就是XDMA 可以提供最多两个独立的写通道和两个独立的读通道,独立的通道对于实际应用中有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。这里我们选择1

Number of Request IDs for Read (Write)channel :这个是每个通道设置允许最大的outstanding 数量,按照默认即可

配置完成以后,点击Run Block Auto,可以看到之前的配置信息,如果有发现和目标配置不一样的,需要手动修改,点击OK,完成配置

配置完成以后,VIVADO 会自动进行必要的连接

到此为止,XDMA IP 配置就完成了只要再进行时钟和GTP约束即可。

1.5 MIG 7 SERIES 的配置

Step1:任单击 IP Catalog,选取 Memory Interface Generator(MIG 7 series)IP 添加到 Block design。双击 MIG 7 SERIES ,对这个 IP 进行配置。

双击生成的IP核

选择Create Design 单击NEXT

继续单击NEXT

选择DDR3 单击NEXT

设置MIG 内核时钟频率、内存型号、内存的数据位宽

设置MIG AXI4 最大支持的位宽,对4于片DDR 最大位宽为512bit

设置输入频率为200M

系统和参考时钟时钟选择no buffer,MIG低电平复位

Step9:终端阻抗选择40hms,设置DCI

选择Fixed Pin Out

根据原理图手动填写PIN 脚定义,或者选择Read XDC/UCF直接读入pin脚定义,本课程下提供了MK7160FA.ucf 的DDR 配置文件,直接读入既可。

填写完成后,先单击Validate再单击NEXT

继续单击NEXT

继续单击NEXT

继续单击NEXT

继续单击NEXT

最后单击Generate,至此MIG的配置完成

1.6基础测试系统搭建

我们的测试目标是进行PCIE AXI4总线与外设进行读写操作,PCIE AXI4-Lite 总线进行用户逻辑寄存器或者其他AXI4-Lite 总线设备访问操作。AXI4总线上挂载到MIG控制器DDR上去,实现对DDR的读写控制。

为此搭建系统为下图所示:

进行地址分配:

这里我们把挂在M_AXI上的DDR地址分配从0开始(对于widnows系统必须为0), M_AXI是需要进行DMA操作的。而M_AXI_LITE挂载的BRAM是需要进行BAR空间操作,所以地址设置为0x80000000和XMDA IP里面设置的地址对应。

1.7WIN7/WIN10系统下开发环境搭建

请用户在我们提供的网盘里面下载 VS2015,WINSDK,WDK 开发包,这是经过我们验证的,如果 SDK 和

WDK 版本不匹配会造成编译失败。

首先是 VS2015 的安装,如果已经安装了 VS2010,或者其他版本,建议先进行卸载,卸载过程不要使用 360

等软件工具卸载,而是使用 VS 自带的卸载工具(注意:操作过程中可能会出现问题,导致该系统无论如何都无法

编译程序,本教程不对此情况负责,我们测试宿主机是一台刚刚安装了 WIN7/WIN10 系统的机器,为了避免因搭建环境而造成宿主机原系统算坏的情况,建议用户可以花几十块钱购买一块 320G 以下的硬盘,在新硬盘安装系统搭建环境测试)

大家请注意软件的安装顺序一定要是先安装vs2015再安装WINSDK,最后安装WDK。如果一不小心顺序错了,卸载干净后重新安装,否则肯定不会成功的。

这里一定要选择自定义,默认情况下是不安装 VC++语言的,不知道VS 是怎么搞的。

然后在编程语言里面勾选 vc++,vs2015 更新 3 也勾选上,否则也可能造成编译错误,这些错误主要是由于版本匹配问题引起的。下面就是一路安装,不多说了。安装好以后,记得去百度搜个序列号,你们懂得。

下面安装WINSDK。

最后安装WDK

接下来还有一项重要的设置,根据官方文档的说法,XDMA 的驱动没有提供一个验证过的证书,所以必须使用

测试模块才能安装驱动。

打开上面的连接,可以看到使用如下命令可以开关测试模式。

另外也可以采用禁用驱动签名的办法来安装没有签名的驱动,禁用驱动签名的办法,下面我们也会演示。首先还是采用测试模式下进行。

bcdedit /set testsigning on 打开测试模式

bcdedit /set testsigning off 关闭测试模式

在 WIN7/WIN10 系统下打开终端,一定要使用管理员权限

显示操作成功,电脑重启,可以在桌面的右下角看到,系统进入测试模式。

1.8 WIN7/WIN10下驱动程序编译以及安装

1.8.1 驱动编译(如果不想编译可以跳过)

Xilinx 提供的XDMA 驱动源码,直接编译可能会由于WPP 的原因导致编译失败,WPP 是驱动调试功能,用户可以自行修改,本教程中不使用 WPP 功能,同时对驱动源码进行了一些修改,可以直接使用,请参考我们提供的工程。工程文件如下:

driver 里面是驱动源码,其他项目都是应用程序。拿到工程以后,先进行清理,然后进行编译。

编译成功。然后可以在如下目录里面看到生成的驱动文件

可以在如下目录看到生成的应用程序文件

1.8.2 驱动安装

和纯FPGA的开发板不一样,ZYNQ一定要先用SDK烧录程序,烧写完成之后重启电脑,打开设备管理器,可以看到被识别倒是未驱动的PCIE 设备。

接下来进行驱动的安装,首先安装证书文件,XDMA.cer,双击安装即可。然后在设备管理器里面选择PCIE 设备,右击

更新驱动程序软件,选择浏览计算机查找驱动程序

选择生成驱动的 sys 目录下面的 XDMA 目录

到此,PCIE 驱动就安装完毕了。

1.9 WIN7/WIN10下 XDMA 应用程序测试

我们打开一个终端(如果双击运行会很快退出来),进入到上一节编译生成的应用程序目录找到xdma_rw.exe,这个应用程序是操作 pcie 的所有设备的,我们在终端只输入xdma_rw.exe,可以看到提示信息,告诉用户这个程序如何使用

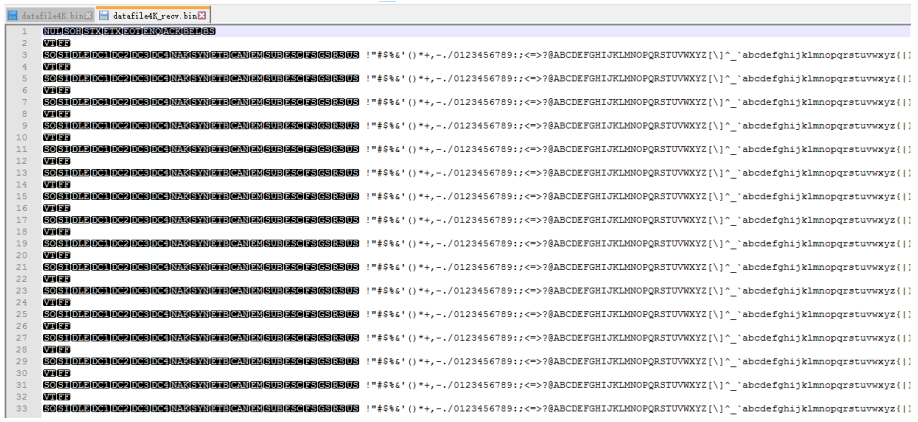

可以看到在当前目录有一个datafile4k.bin文件,那就测试一下将这个文件传输到 FPGA(BRAM),然后读出来。首先在终端输入指令:xdma_rw.exe h2c_0 write 0x0000000 -b -f datafile4K.bin -l 4096 意思就是使用h2c_0 设备以二进制的形式读取文件datafile4k.bin写入到BRAM内存地址0x0000000长度为4096字节。

接下来再读回来,使用命令 xdma_rw.exe c2h_0 read 0x0000000 -b -f datafile4K_recv.bin -l 4096

接下来我们可以使用 winhex 等软件来检查一下两个文件数据是否一直,经过检查,是一致的则说明传输功能正常。